Introduction

A la différence d’un circuit combinatoire, l’état d’un circuit séquentiel dépend de l’état de ses entrées et de l’état précédent de ses sorties ; il doit donc "se rappeler" ou avoir de la "mémoire". Par mémoire, on exprime le phénomène qui consiste à conserver l’effet d’un événement après sa disparition.

Objectifs.

-

Comprendre le principe de la mémorisation en logique séquentielle.

-

Comprendre le fonctionnement d’une mémoire élémentaire, la bascule.

-

Découvrir plusieurs principes de bascules et leurs applications.

-

Réaliser une fonction comptage.

-

Réaliser un registre et des mémoires.

-

Intégration de fonctions complexes dans des circuits logiques programmables.

Principe de mémorisation.

Prenons l’exemple simple de la commande d’une perceuse à colonne.

-

Un bouton permet de mettre en marche la machine

-

Un bouton permet de l’arrêter.

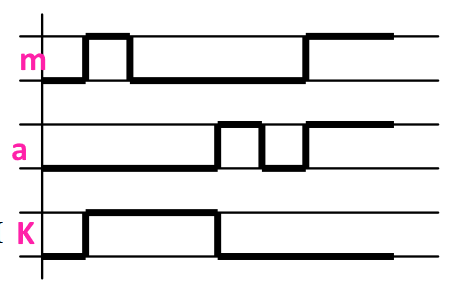

Quand on appuie sur le bouton "marche", le moteur démarre, quand on relâche le bouton, le moteur continue à tourner. L’ordre de mise en marche a donc été mémorisé. Il en est de même pour le bouton "arrêt". L’action arrêt est prioritaire : si m et a sont appuyés en même temps, on arrête le moteur.

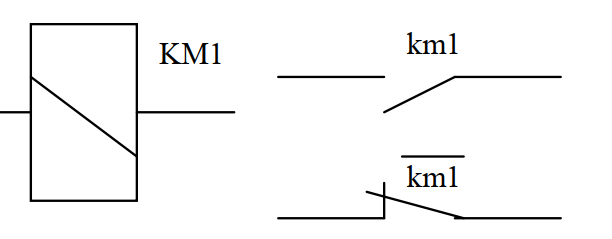

Le contacteur.

C’est un appareil composé d’une bobine (électroaimant) qui lorsqu’elle est parcourue par un courant électrique agit sur un ou plusieurs contact.

Si le relais s’appelle KM1, tous les contacts issu de ce relais portent le même nom et changeront d’état en même temps.

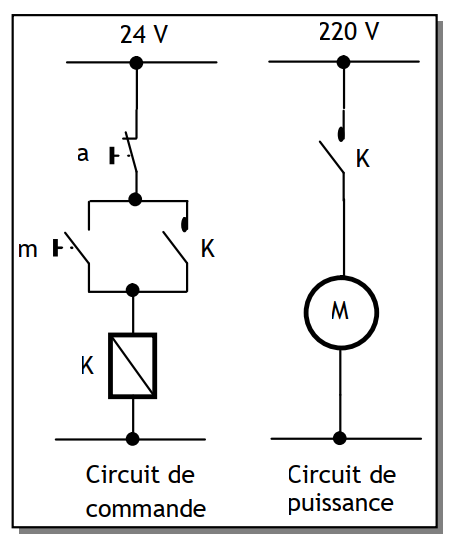

Mémoire élémentaire en technologie électrique à arrêt prioritaire.

-

Le bouton m est un contact ouvert au repos ; le bouton a est un contact fermé au repos. Le relais K dispose de 2 contacts : un utilisé dans le circuit de commande et l’autre utilisé dans le circuit de puissance.

-

Quand l’utilisateur appuie sur m, la bobine du relais est alimentée. Les contacts K associés se ferment. Si l’utilisateur relâche m, le courant continue à circuler par K ; le relais est alors auto-alimenté et le moteur continue à tourner. L’équation du relais X et du moteur M est :

|

nous avons l’équation:

\$ K =(K+m).bar(a)\$

|

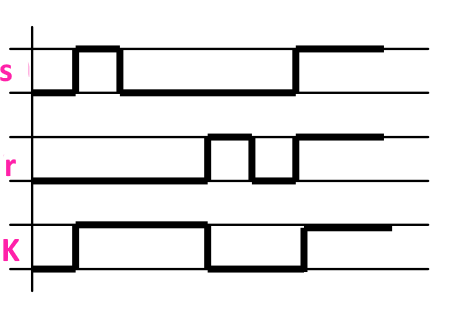

Chronogramme arrêt prioritaire.

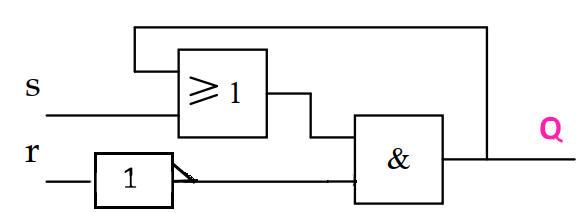

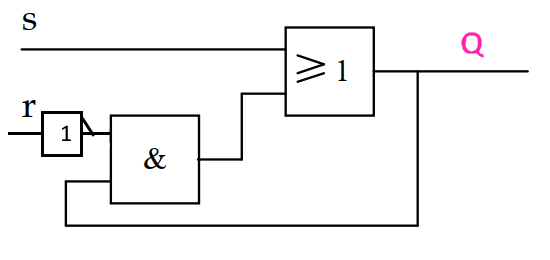

Logigramme équivalent avec des portes logiques.

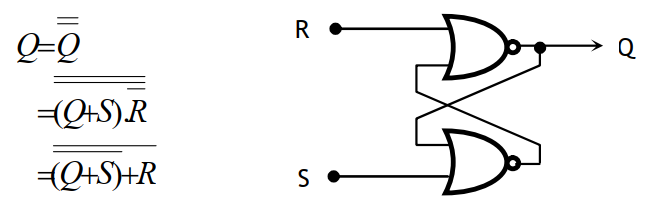

Si on fait la correspondance logique : S correspond à m, R correspond à a et Q correspond à K. On en déduit alors l’équation avec la notation utilisée pour les mémoires numériques élémentaires, appelées bascules avec Reset prioritaire.

Passage en NOR (Non OU):

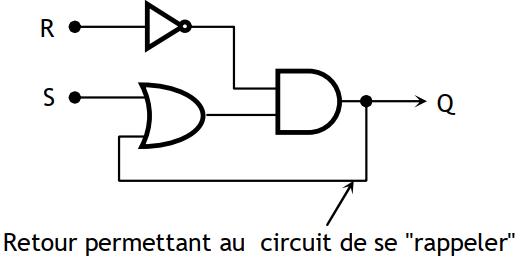

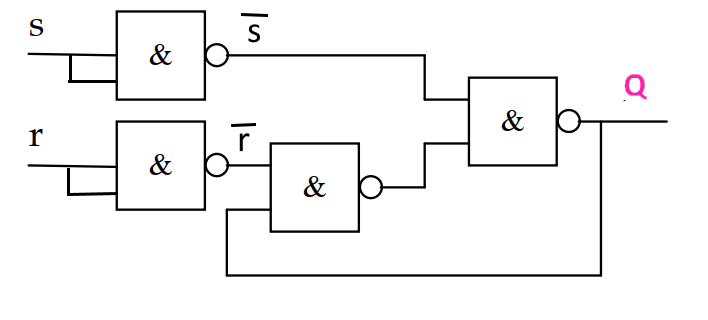

Nous pouvons remplacer le logigramme précédent avec 2 portes identiques de type NOR. D’une manière générale afin de limiter les coûts et la logistique, on essaie d’utiliser des composants identiques.

|

Nous allons utiliser le théorème de Morgan pour le passage en NOR |

Approche par une étude de la logique combinatoire classique.

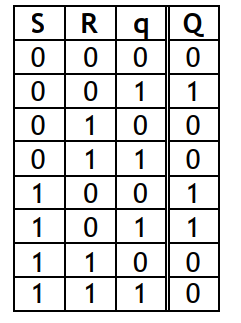

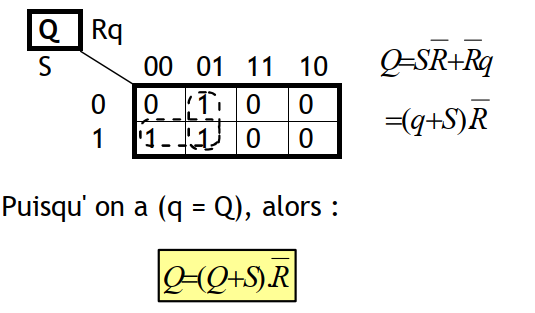

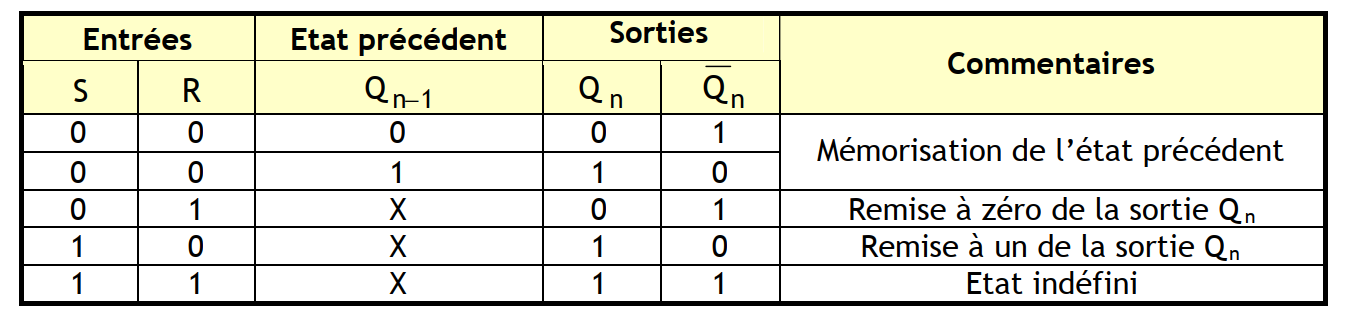

Table de vérité:

Dans cette approche, on raisonne comme pour un circuit combinatoire. Il est donc nécessaire de connaître l’état de Q pour connaître l’état de la sortie lorsque les deux entrées sont à 0 (état de mémoire). On introduit alors une variable supplémentaire qui indique l’état précédent de Q. On note "q" cette variable.

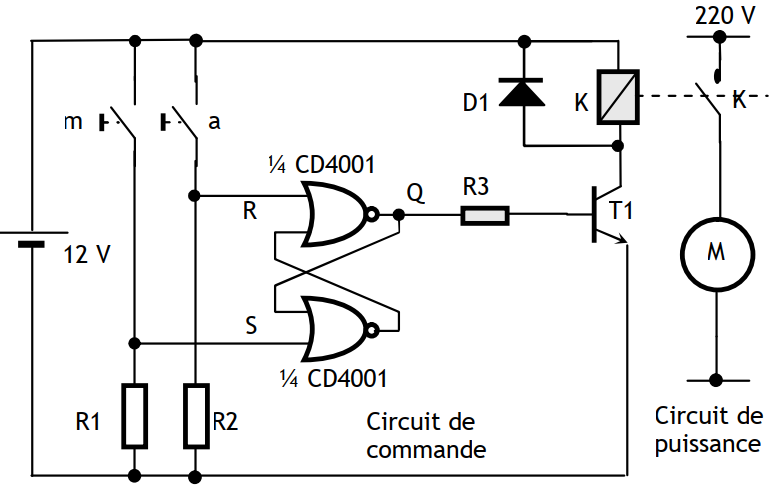

Synthèse: Nouveau schéma de la commande de la perceuse.

Il s’agit de trouver la version électronique du montage Marche/Arrêt du moteur ; le circuit utilisé est le circuit CMOS CD4011 comportant 4 portes NOR à 2 entrées.

La marche prioritaire?

Nous pouvons également réaliser des mémoires à marche prioritaire.

Nous pouvons déduire l’équation logique suivante:

Avec une adaptation à la notation électronique:

En utilisant le théorème de Morgan, nous pouvons passer le montage avec des portes NAND uniquement.

\$ Q = bar(bar (s).bar(bar(r).q))\$

Les Bascules: mémoire élémentaire.

Comme les opérateurs logiques élémentaires en logique combinatoire, les bascules (appelées aussi flip-flop) sont les éléments de base de la logique séquentielle.

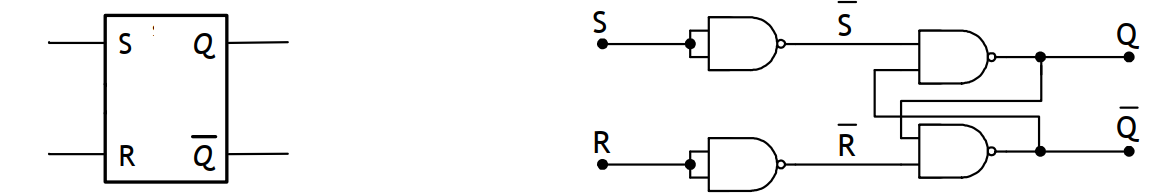

Bascule RS Asynchrone:

Les bascules RS sont à la base de tous les éléments de mémorisation. Il s’agit d’un montage utilisant deux portes NAND et capable de mémoriser un niveau logique choisi à l’aide de deux sorties complémentaires. Son schéma est donné à la figure 1 :

La table de vérité d’une telle bascule est la suivante :

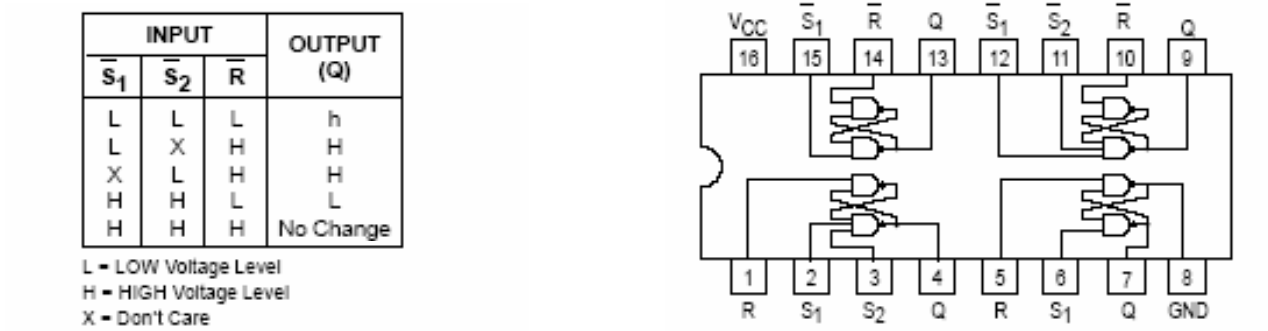

Parmi les circuits intégrés à bascules , on trouve le 74279 dont la table de fonction et le schéma de brochage sont donnés à la figure suivante:

|

Cette bascule présente deux inconvénients majeurs :

|

Exercices:

Compléter les fiches d’éxercices suivantes:

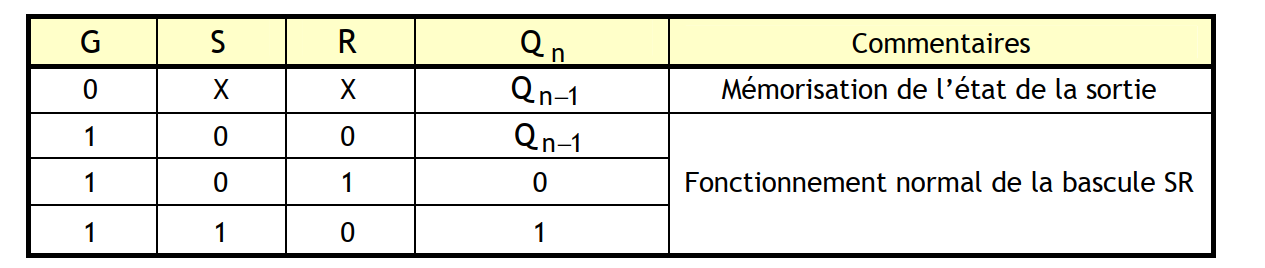

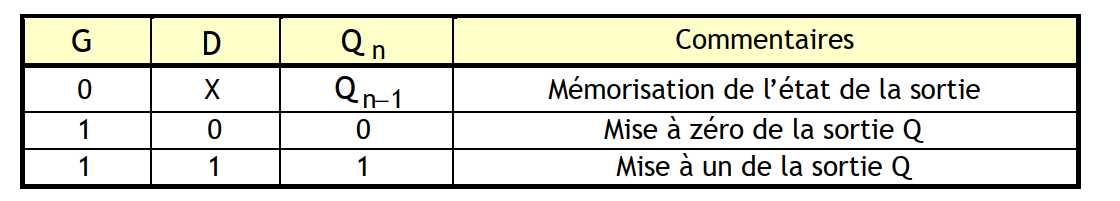

Bascule RS synchrone:

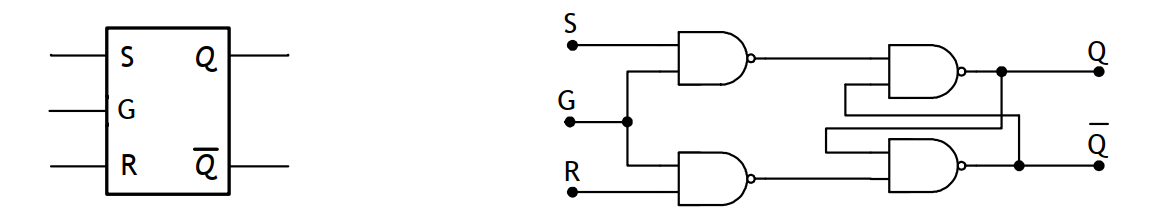

La bascule SR synchrone permet de résoudre le premier inconvénient de la bascule RS asynchrone. Les ordres Set et Reset ne changent l’état de la sortie qu’après l’autorisation d’un signal de commande G (Gate) ou C(pour clock) :

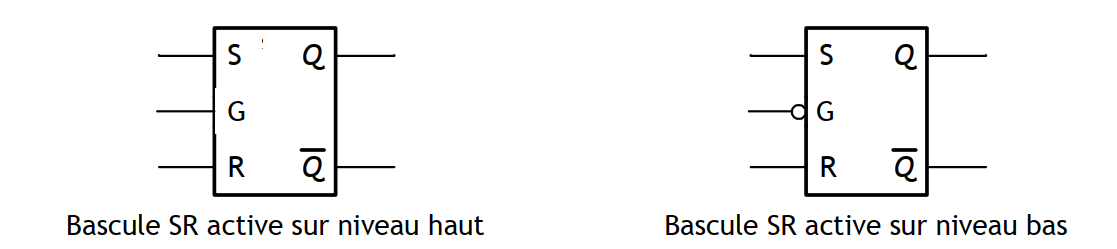

Le changement d’état de cette bascule est autorisé sur niveau logique 1 du signal de commande G. On dit que c’est une bascule commandée de manière statique (sur niveau logique 0 ou 1) et sa représentation est donnée à la figure suivante:

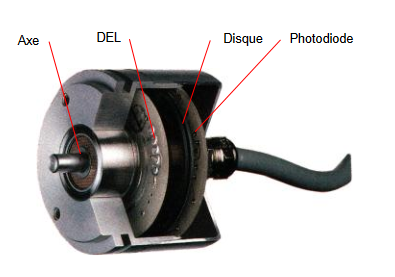

Bascule D:

La bascule D est dérivée de la bascule RS en ajoutant un inverseur entre Set et Reset pour n’avoir plus qu’une seule entrée pour fixer le niveau à mémoriser. Avec un tel montage, il n’y a plus de combinaisons d’entrées invalides (S=R=1) :

Le changement d’état d’une bascule D peut aussi être autorisé par le front montant ou le front descendant du signal de commande G ou C. On parle alors de bascule D dynamique.

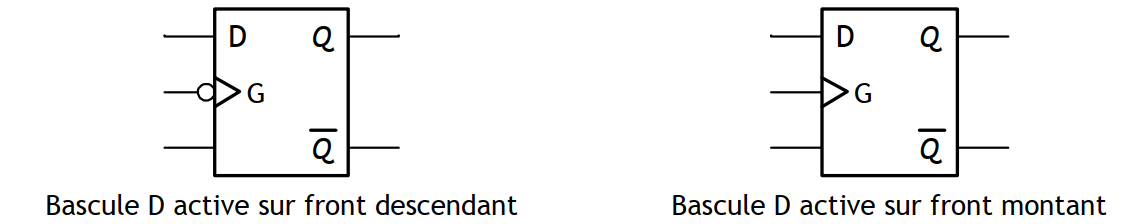

Parmi les circuits intégrés à bascules D, on trouve le 7475 dont la table de fonction et le schéma de brochage sont donnés par la figure suivante:

Exercices:

Compléter les fiches d’éxercices suivantes:

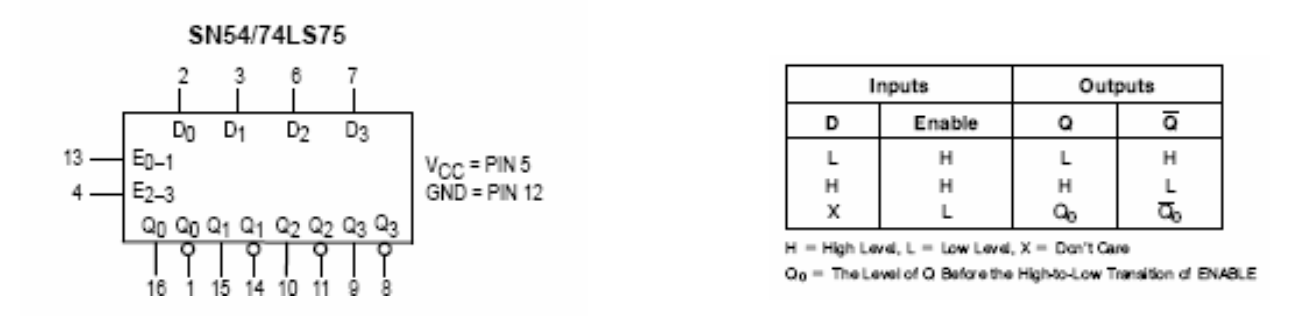

Application: Détection du sens de rotation d’un moteur.

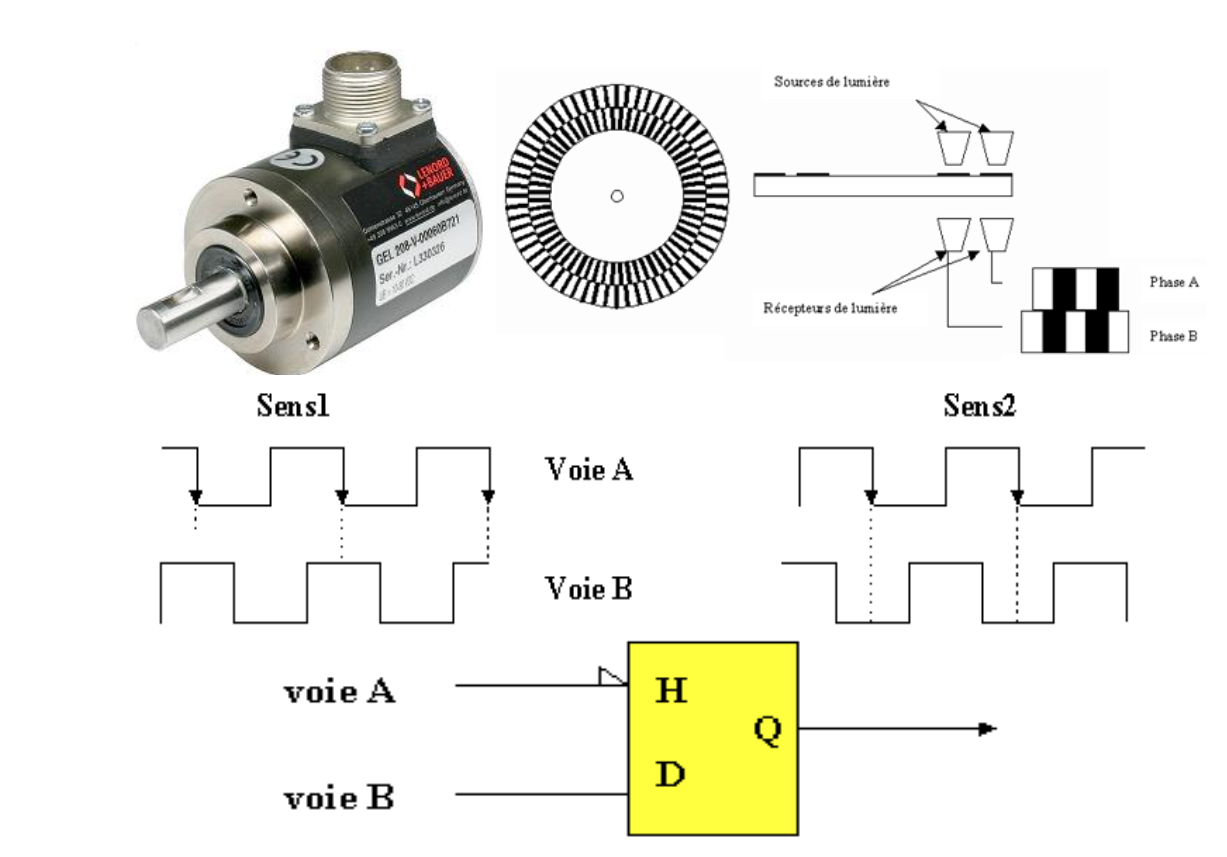

Pour contrôler la position et la vitesse d’un bras de robots, on utilise souvent des codeurs optiques rotatifs, fixés à l’extrémité de l’axe de transmission de mouvement comme un codeur incrémental.

Le codeur incrémental.

Le disque d’un codeur incrémental comporte 3 pistes:

-

Deux pistes A et B divisées en «n» intervalles d’angles égaux et alternativement opaques et transparents. «n» permet de définir la résolution ou période.

-

La piste A est décalée de ¼ de période par rapport à B. Le déphasage entre A et B permet de définir le sens de rotation.

Deux photodiodes délivrent des signaux carrés pour les pistes A et B chaque fois que le faisceau lumineux traverse une zone transparente. Une piste Z comporte une seule fenêtre transparente. Le signal Z appelé «top zéro» est synchrone avec les signaux A et B. Il définit une positionde référence et permet la réinitialisation chaque tour.

Avec l’utilisation d’une bascule D telle que sur le schéma précédent, on constate que la sortie Q sera toujours dans un même état pour un sens de rotation et dans un autre pour le sens inverse.

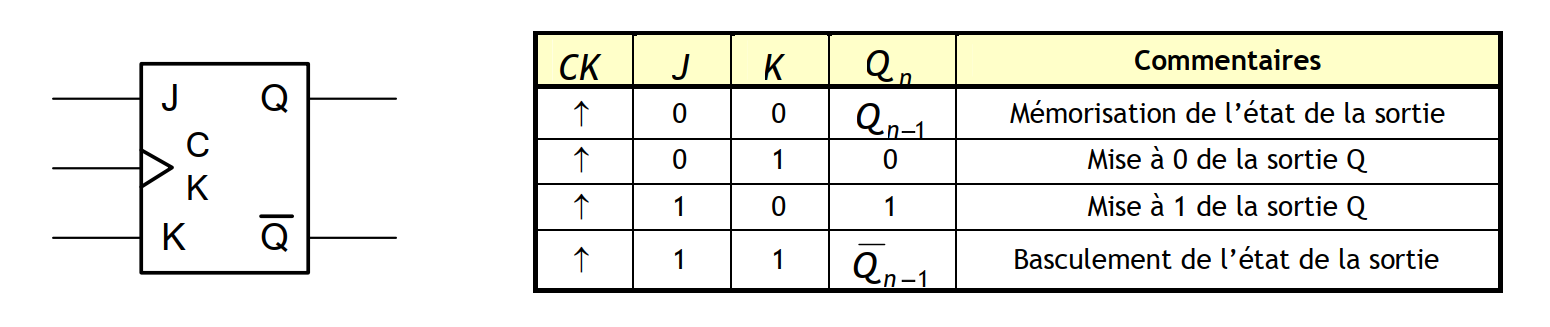

Bascule JK:

Le principe des bascules dynamiques permet de mieux protéger la bascule contre les changements indésirables des entrées. La bascule JK permet en plus de lever l’ambiguïté qui existe pour l’état S=R=1 d’une bascule SR. Son symbole et sa table de vérité sont les suivants :

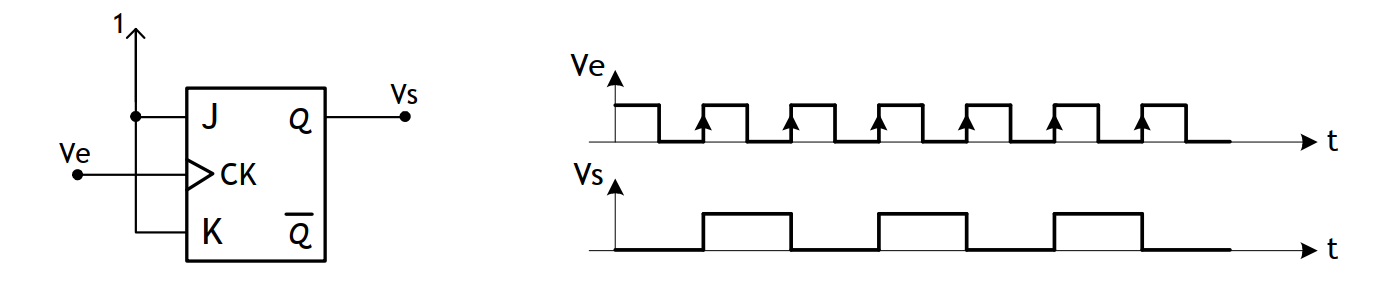

Si on utilise la bascule JK avec J = K = 1, on obtient l’une des principales applications de la bascule JK à savoir le diviseur de fréquence par 2.

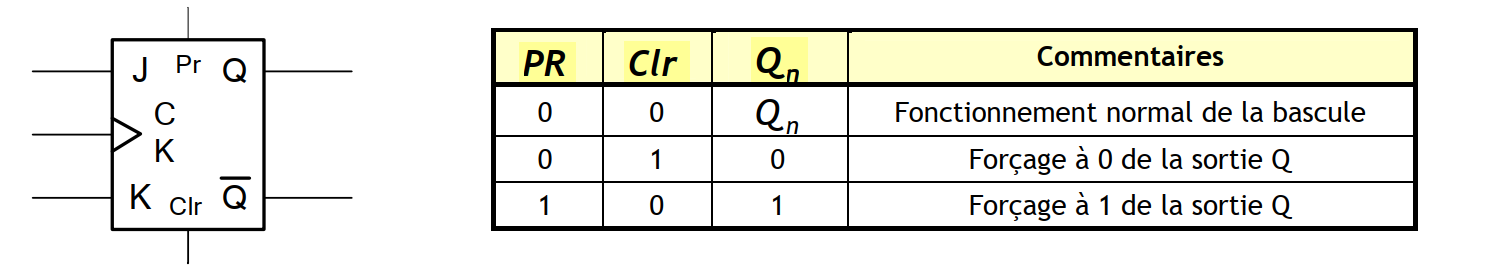

Fonctionnement forcé des bascules:

Il est parfois nécessaire d’affecter le niveau de sortie d’une bascule de manière non synchrone c’est-à-dire indépendamment de l’horloge. C’est le rôle des entrées de forçage asynchrone Preset (Set) et Clear (Clr) qui permettent d’initialiser la bascule :

Les compteurs.

Un compteur est un ensemble de n bascules interconnectées. En effet, nous avons vu dans la construction des tables de vérité que pour passer d’un poids binaire au poids binaire de rang supérieur, il suffit de diviser par 2. Donc en plaçant des bascules en cascade, nous pouvons compter.

-

Le nombre de bascules en cascade donne la capacité de comptage. Exemple, pour 3 bascules montées en diviseur par 2 on ne peut compter que jusqu’à 7.

-

Cette capacité de comptage s’appelle le modulo, dans notre exemple précédent le modulo est 8 et on compte de 0 à 7.

|

Avec cette mise en cascade seule, on ne peut pas compter de 0 à 9 car le modulo 10 n’est pas une puissance de 2. |

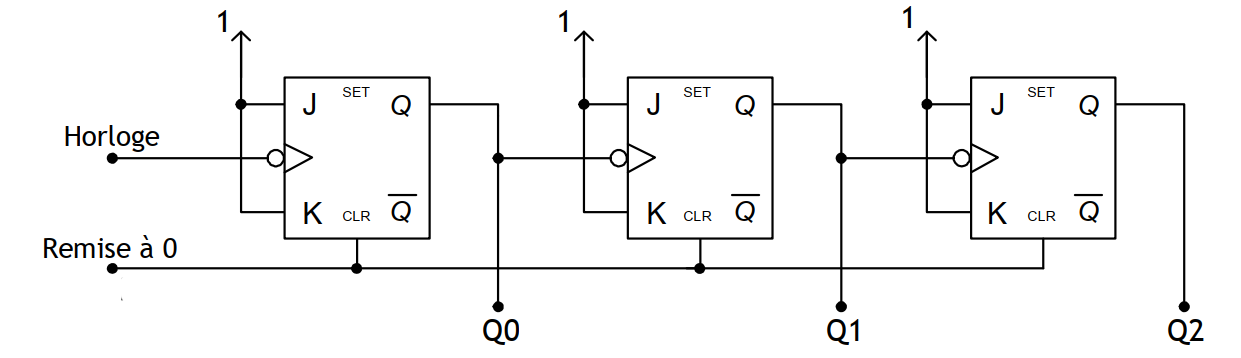

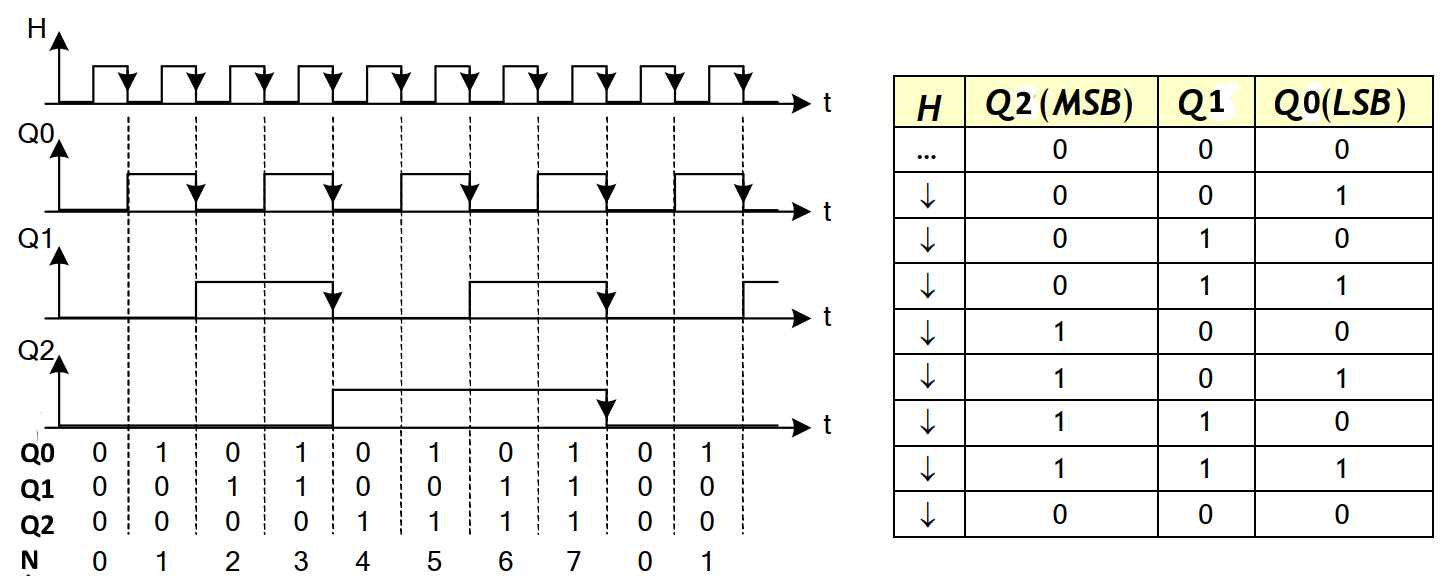

Compteur asynchrone modulo N=2 n

Ce type de compteur est constitué de n bascules JK fonctionnant en mode T (Toggle) : J=K=1. Ces bascules sont montées en cascade c’est-à-dire le signal d’horloge commande uniquement la première bascule tandis que pour chacune des autres bascules le signal d’horloge est fourni par la sortie de la bascule de rang immédiatement inférieur. Pour bien comprendre le principe, réalisons un compteur modulo 8 permettant de compter de 0 à 7 comme le montre la figure suivante:

Compteur asynchrone modulo N quelconque.

Pour ce type général de compteur qui compte de 0 à N-1, on va étudier l’exemple d’un compteur asynchrone modulo 10 (0 à 9). Pour le réaliser, il y a deux étapes :

-

On cherche d’abord la puissance de 2 immédiatement supérieure à N et qui est pour notre compteur 24 = 16. L’exposant de cette puissance de 2 donne le nombre de bascules JK à monter en cascade, 4 pour notre exemple ;

-

On détecte ensuite l’état N qui remettra le compteur à 0 et qui est pour notre compteur 10 = \$(1010) underset(2)\$. On relie les sorties Q = 1 (Q1 et Q3) pour N aux entrées d’une porte NAND dont la sortie commandera l’entrée CLR de chaque bascule .

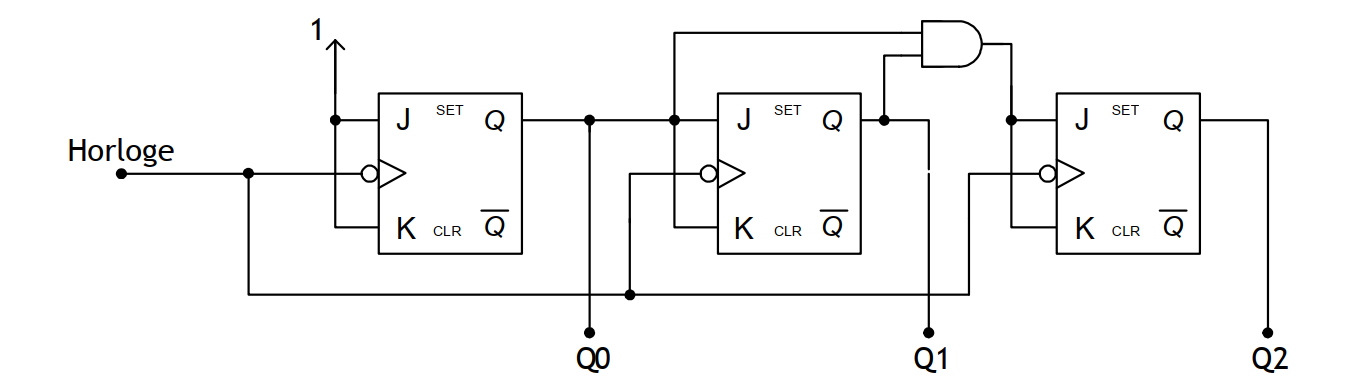

Compteurs synchrones.

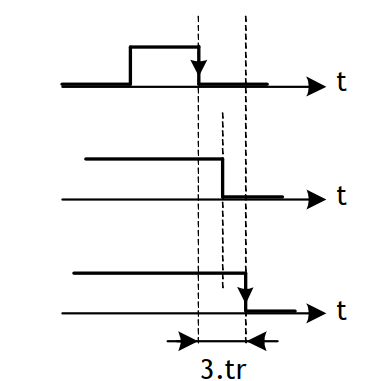

L’inconvénient du compteur asynchrone c’est le temps de réponse de chaque bascule. Ainsi, le signal d’horloge ne parvient pas simultanément sur toutes les bascules. Ceci a pour conséquence de provoquer des états transitoires qui peuvent être indésirables.

Supposons un temps de réponse tr identique pour toutes les bascules et considérons la chronologie du passage d’un compteur asynchrone 3 bits de 111 à 000 dans la figure ci-contre. Nous constatons que le compteur passe par les états transitoires 011 et 001 qui sont faux en plus d’un temps de propagation qui a triplé.

Dans un compteur synchrone toutes les bascules reçoivent en parallèle le même signal d’horloge. Pour faire décrire au compteur une séquence déterminée il faut à chaque impulsion d’horloge définir les entrées synchrones J et K.

Compteurs synchrones intégrés.

Nous allons étudier à travers plusieurs exercices, différents types de compteurs intégrés synchrones vendus dans le commerce.

Exercices:

Compléter les fiches d’éxercices suivantes:

Les registres

les registres de mémorisation.

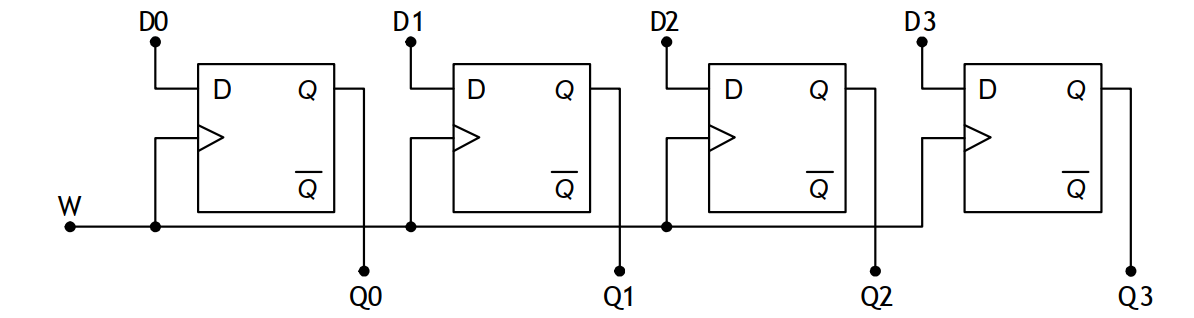

Un registre est constitué d’un assemblage de n bascules D permettant la mémorisation temporaire de n bits avec ou sans décalage. L’information est emmagasinée sur un signal de commande et ensuite conservée et disponible en lecture. La figure suivante donne un exemple de registre de mémorisation 4 bits avec le signal d’écriture W (Write) qui commande la mémorisation des données D0, D1, D2 et D3:

Les registres à décalage:

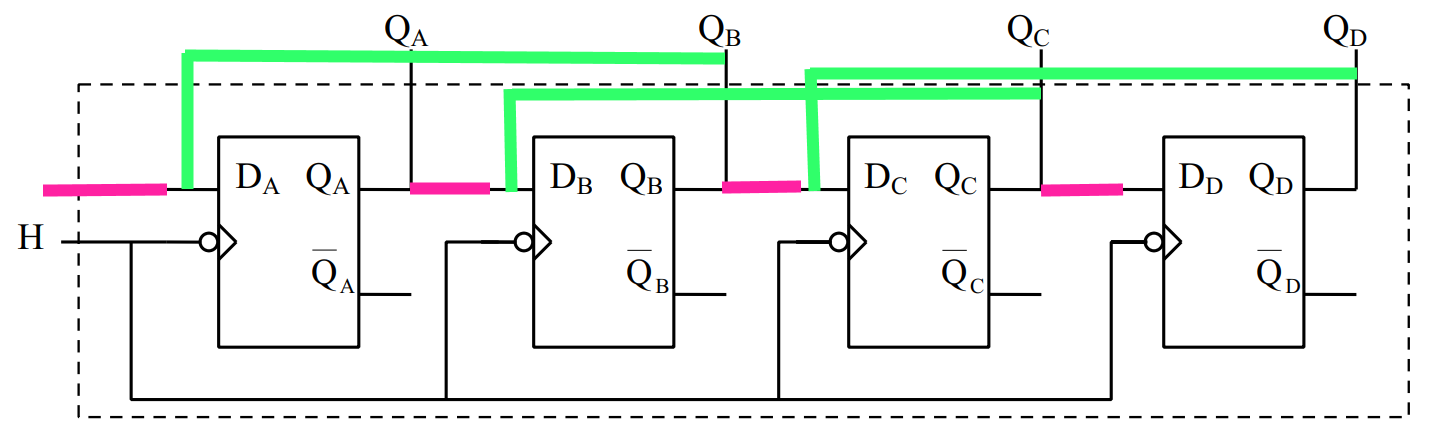

Si l’on veut pouvoir transférer les données d’une case mémoire dans celle de droite ou de gauche, il faut interconnecter les bascules entre elles : on obtient alors un registre à décalage.

Par exemple, on voit dans le schéma ci-dessus que, si on relie QA à DB, QB à DC et QC à DD, on obtient un registre à décalage à droite(connexions en rouge), c’est à dire qu’à chaque impulsion de l’horloge, le bit contenu dans la bascule A sera transféré dans B, celui contenu dans B sera transféré dans C et ainsi de suite.

Si l’on veut obtenir un registre à décalage à gauche, il faut relier QD à DC, QC à DB et QB à DA(connexion en vert).

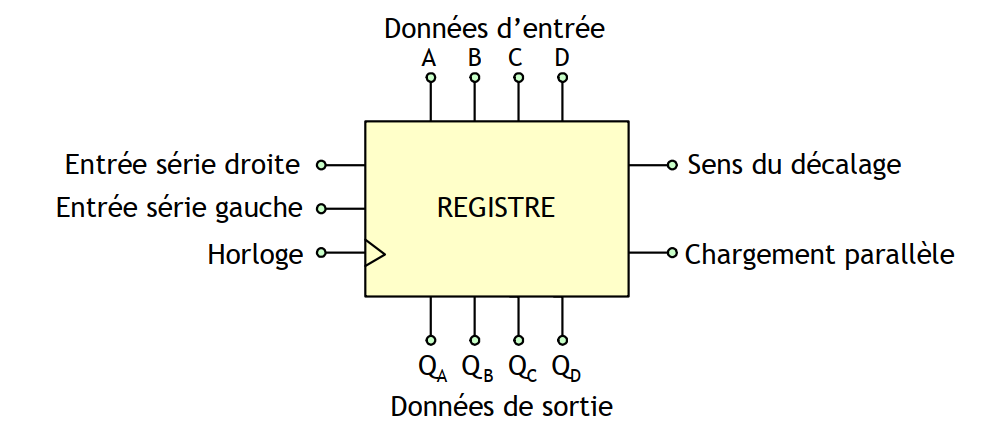

A partir de ce principe, on peut compléter le schéma pour obtenir un registre permettant soit le décalage à droite, soit le décalage à gauche, soit le chargement parallèle (4 valeurs binaires a, b, c et d sont mémorisées dans les 4 bascules, sur la même impulsion d’horloge), soit la mémorisation (les données mémorisées ne changent pas au moment des impulsions d’horloge). Un tel registre est dit "registre universel".

Pour obtenir ces 4 modes différents de fonctionnement, il faudra bien sur disposer de 2 entrées de commande pour choisir l’un d’entre eux.

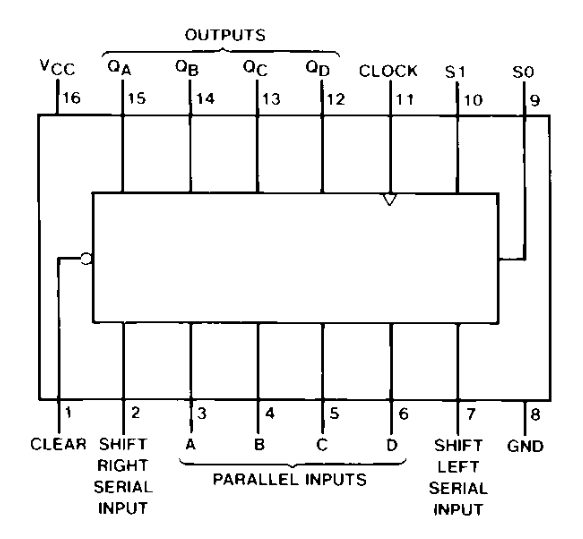

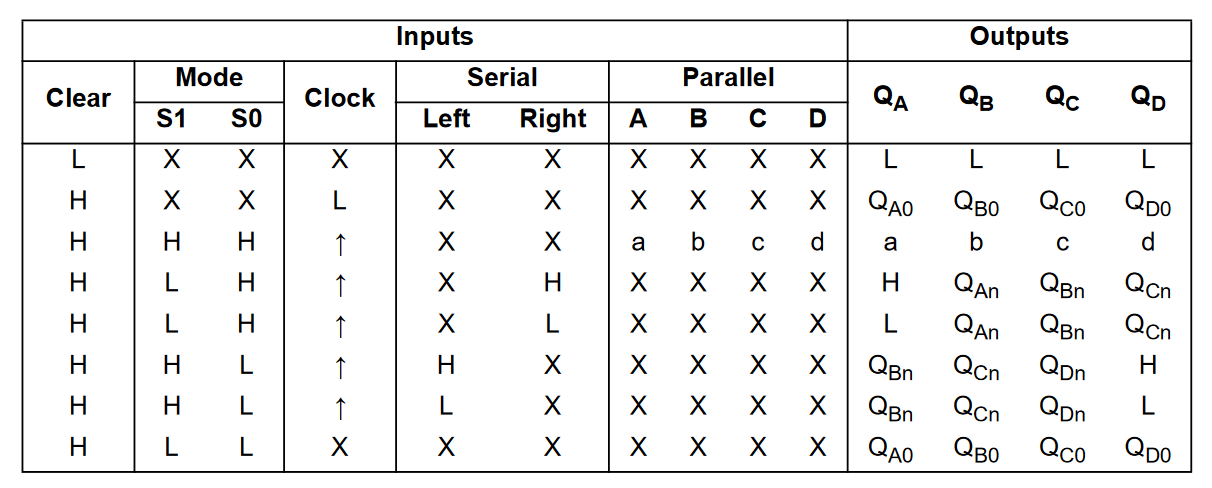

Parmi les registres universels, on trouve le 74194 qui est un registre à chargement parallèle ou série, avec la possibilité d’un déplacement de l’information vers la droite (QA vers QD) ou la gauche (QD vers QA).

Applications.

-

Communication série-parallèle entre une souris,un clavier et un ordinateur.

-

Toutes les communications entre matériels informatiques( tablettes, smartphone…)

-

Faire une multiplication (ou division) par 2 : pour multiplier (ou diviser) un nombre par 2 il faut envoyer un "0" sur DA (ou sur DD)et décaler tous les autres bits vers la droite (ou la gauche).

-

Ligne à retard numérique : si l’on veut retarder une donnée de n tops d’horloge, il suffit de l’envoyer sur DA et de la lire sur la sortie de la nième bascule, en mode décalage à droite.

Les mémoires.

Les systèmes modernes sont souvent à microprocesseur de tels systèmes exigent une capacité mémoire importante pour le stockage des données. Les mémoires électroniques ou à semi-conducteurs sont les éléments qui répondent à ce besoin. Une mémoire est un dispositif capable d’emmagasiner puis de restituer une information. L’unité d’information (bit, octet, etc.) s’appelle «cellule».

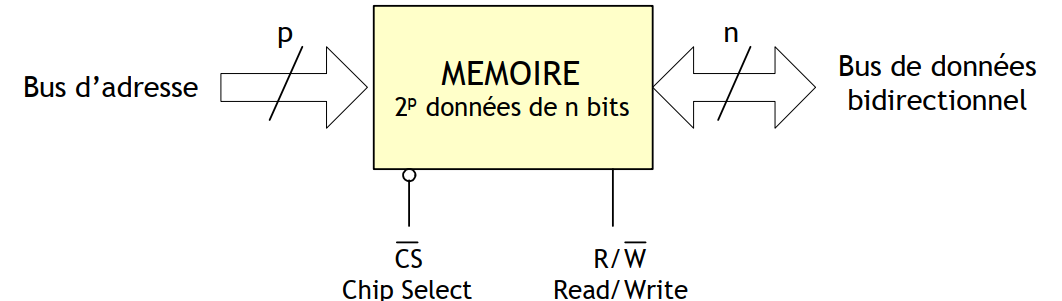

-

L’adresse fournie par le bus d’adresses est le mot binaire de p bits qui permet de localiser la donnée.

-

La donnée de n bits entre (écriture) et sort (lecture) par le bus de données qui est bidirectionnel : deux sens possibles, en liaison avec le signal R/W.

-

La mémoire peut stocker 2 p données de n bits chacune.

-

Le signal CS permet la sélection du circuit ou le mettre en haute impédance ; cette possibilité permet, comme on le verra, l’extension de la capacité mémoire d’un système.

On peut donc utiliser une mémoire soit en :

-

lecture :

-

Appliquer le mot adresse sur le bus d’adresse ;

-

Sélectionner le boîtier mémoire en appliquant un niveau logique bas sur la ligne CS ;

-

Sélectionner le mode lecture en appliquant un niveau logique haut sur la ligne R/W ;

-

-

écriture :

-

Appliquer le mot d’adresse sur le bus d’adresse ;

-

Le mot de donnée sur le bus de données ;

-

Sélectionner le boîtier mémoire en appliquant un niveau logique bas sur la ligne CS ;

-

Sélectionner le mode écriture en appliquant un niveau logique bas sur la ligne R/W ;

-

Caractéristiques des mémoires.

-

La capacité : c’est la quantité d’information qui peut être stockée dans la mémoire. Elle s’exprime en bits ou en mots de n bits. Par exemple :

-

64b, 4Kb, 8Ko (o : octet ou byte ) avec 1o = 8b ; on rappelle qu’en base 2, 1K = 2 10 = 1024 ; 1M = 2 20 = 1048576.

-

-

L’organisation : elle définit le nombre de mots et la longueur de chaque mot. Par exemple :

-

Une mémoire de 64Kx 1 est constituée de 65536 mots de 1 bit. Sa capacité est donc de 64Kb (8Ko) ;

-

Une mémoire de 8Kx8 contient 8192 mots de 8 bits. Sa capacité est de 64Kb (8Ko) ;

-

-

Le temps d’accès : c’est le temps qui s’écoule entre une demande d’information et le moment où elle est effectivement disponible.

-

Temps de lecture (qq ns)

-

Temps d’écriture (de qq ns à qq ms)

-

Temps d’effacement (de qq ns à qq ms)

-

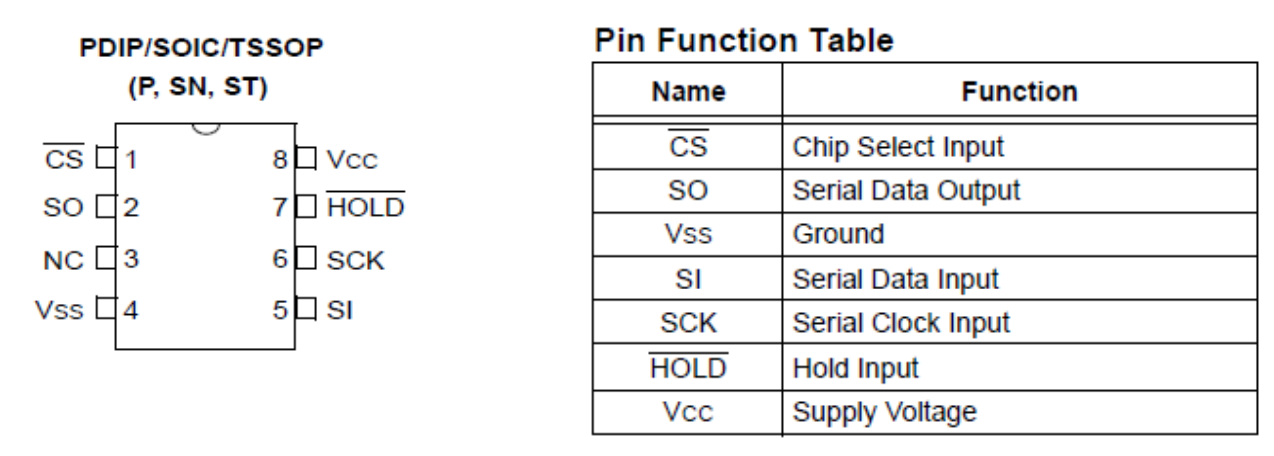

-

Bus de données soit série (avec protocole de communication :

-

SPI, I2C, etc) soit parallèle.

-

-

Tension de programmation (peut aller jusqu’à 21 V)

-

Durée de conservation des données (Data retention) en année (on arrive à des durées > 200 ans pour les ROM)

Les différents types de mémoires.

Les mémoires sont classées suivant deux familles :

-

Mémoires mortes (ROM pour Read Only Memory) : mémoire à lecture seule;

-

Mémoires vives (RAM pour Random Access Memory) : mémoire à lecture et écriture.

Les mémoires mortes.

Les ROM sont utilisées pour stocker des informations figées telles que des programmes fixes dans des machines programmées ou les tables de conversion de données. Le contenu est fixé à la construction ou par l’utilisateur et la disparition de l’alimentation électrique n’altère pas le contenu.

Les mémoires vives.

Dès qu’un système doit conserver temporairement des informations, la RAM trouve sa place. En informatique, elles sont largement mises en oeuvre et en quantités importantes.

Les mémoires programmables et effaçables par l’utilisateur.

Les mémoires programmables sont intermédiaires entre les RAM et les ROM. Leur contenu peut être défini par l’utilisateur et subsister sans alimentation électrique. On en rencontre de différentes familles :

-

Les PROM (Programmable ROM) : sont composées de fusibles que l’on peut détruire une seule fois ;

-

Les EPROM (Erasable PROM) : ce sont des mémoires effaçables par ultraviolet et programmables électriquement ;

-

Les EEPROM (Electrical Erasable PROM) : ce sont des mémoires effaçables et programmables électriquement .

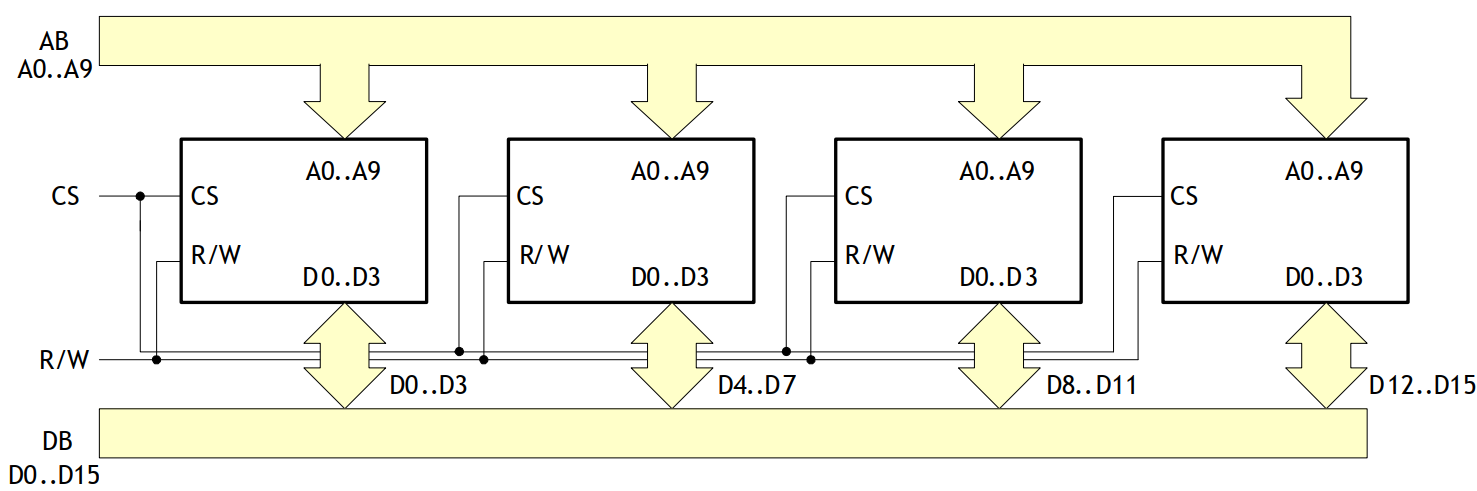

Extension de capacité

Il est courant dans un système microinformatique de grouper plusieurs circuits pour augmenter la capacité (nombre des mots et/ou longueur des mots). Par exemple, à l’aide de 4 boîtiers mémoires de 1Kx4bits, on peut réaliser les mémoires suivantes : 1Kx16bits, 4Kx4bits, 2Kx8bits.

Le schéma de la figure suivante réalise une mémoire de 1Kx16bits à partir d’une mémoire élémentaire de 1Kx4bits :

-

Nécessité de 4 boîtiers ;

-

Nécessité de 10 bits d’adresses A0 à A9 ; (nombre de mots = 2nombre_bits_d’adresse )

-

Nécessité de 16 bits de données D0 à D15 ;

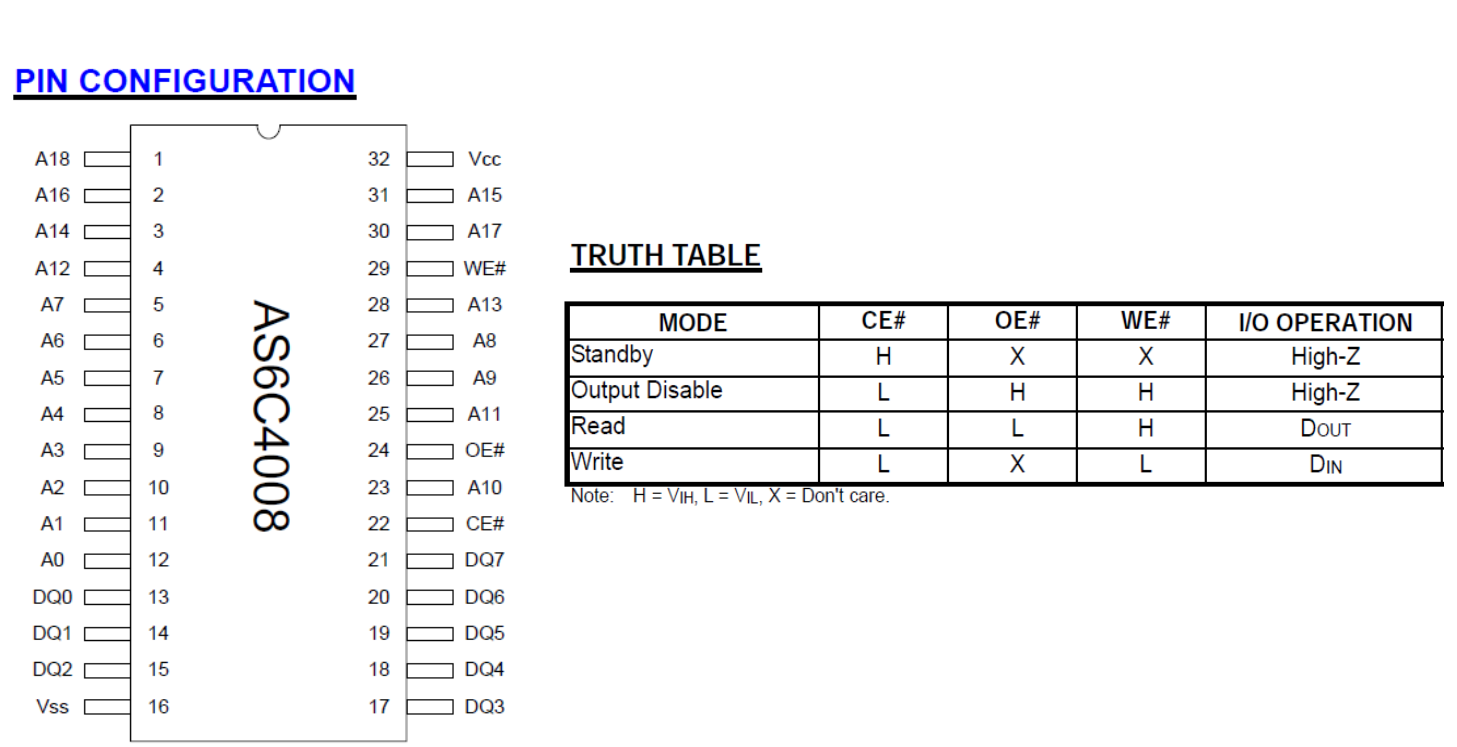

Exemples:

Les composants logiques programmables.

Actuellement les systèmes techniques utilisent de plus en plus de circuits numériques, qui impliquent l’utilisation d’un nombre important de circuits intégrés logiques. Ceci a pour conséquence, une mise en oeuvre complexe, un circuit imprimé de taille importante et un prix de revient élevé. Le développement incessant de la technologie des mémoires électroniques utilisées en informatique a alors permis la naissance des circuits logiques programmables (Programmable Logic Devices ou en abrégé PLD ).

Principes

Un circuit programmable est un assemblage de circuits de base qui sont génériques (opérateurs logiques combinatoires, multiplexeurs, bascules, etc.). On trouve en particulier dans un PLD :

-

des multiplexeurs permettant la création de chemins entre ses différents composants ;

-

des OU Exclusif permettant la complémentarité des fonctions ;

-

des bascules généralement de type D, permettant la mémorisation des fonctions ;

-

et des réseaux logiques programmables qu’on détaille ci-après.

|

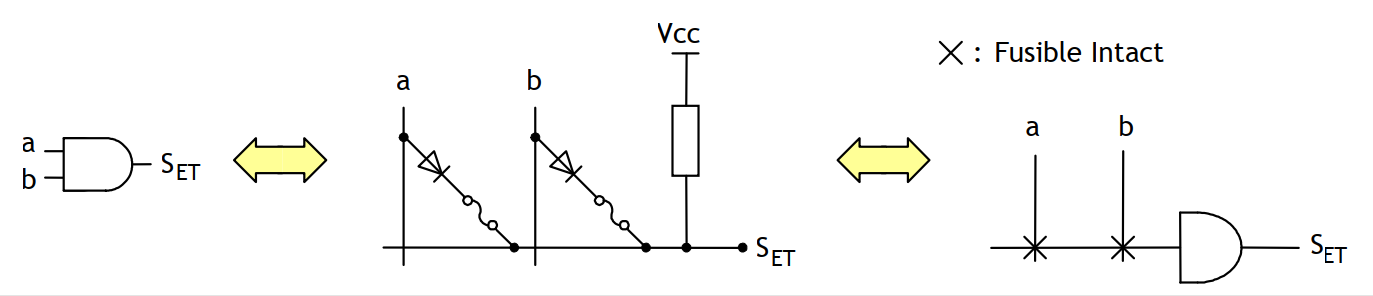

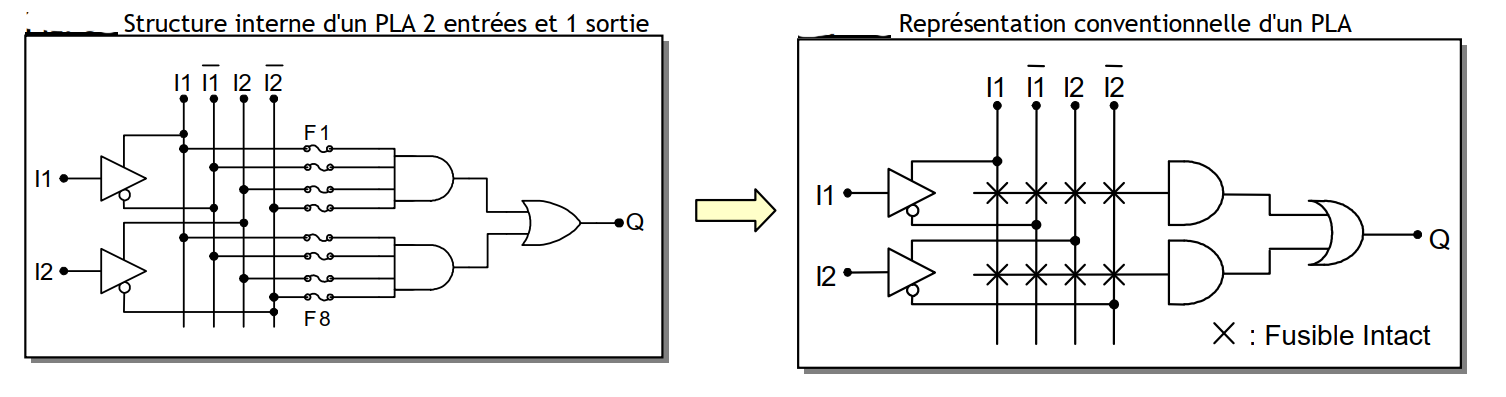

Toute fonction logique combinatoire peut se mettre sous forme d’une somme (OU) de produits (ET). |

Partant de ce principe, on en déduit une structure appelée PLA (Programmable Logic Array). Elle est constituée :

-

D’un ensemble d’opérateurs « ET » sur lesquels viennent se connecter les variables d’entrée et leurs compléments ;

-

D’un ensemble d’opérateurs « OU » sur lesquels les sorties des opérateurs « ET » sont connectées.

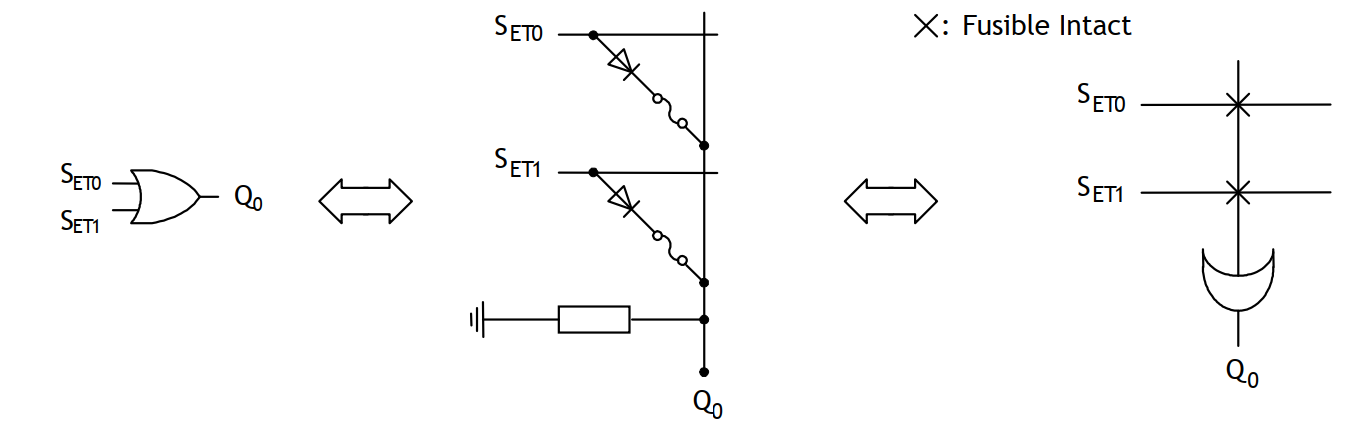

L’ensemble des opérateurs forment des matrices (matrice OU et matrice ET). Les interconnexions de ces matrices sont assurées par des fusibles qui sont « grillés » lors de la programmation. Lorsqu’un PLD est vierge toutes les connexions sont assurées (fusibles intacts). Les figures suivantes représentent la structure interne d’un PLA et sa représentation simplifiée d’une telle structure :

Pour matérialiser les interconnexions :

-

la technique des fusibles est en voie de disparition ; en effet, dans cette technique, on l’aura compris, le PLD est programmé un fois pour toutes ;

-

Parmi les techniques utilisées actuellement, on retient celle qui est la plus courante ; il s’agit de la technique utilisant le transistor "MOS à grille isolée". Cette technique permet de programmer et reprogrammer le PLD. Le circuit est donc effaçable électriquement. De point de vue aspect physique, le fusible est tout simplement remplacé par un transistor MOS à grille isolée.

Exemple simple d’utilisation.

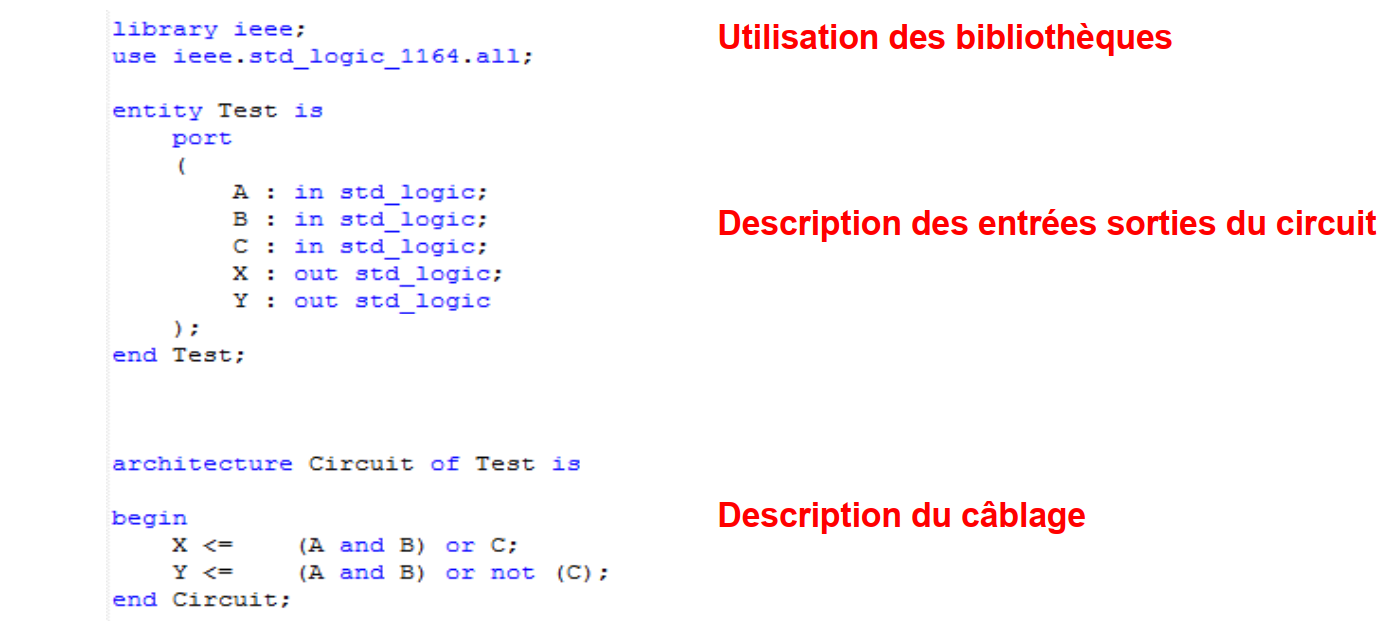

Conception.

Bien que ces circuits peuvent réaliser des projets particulièrement complexes, nous allons faire un exemple simple pour comprendre le processus de dévéloppement.

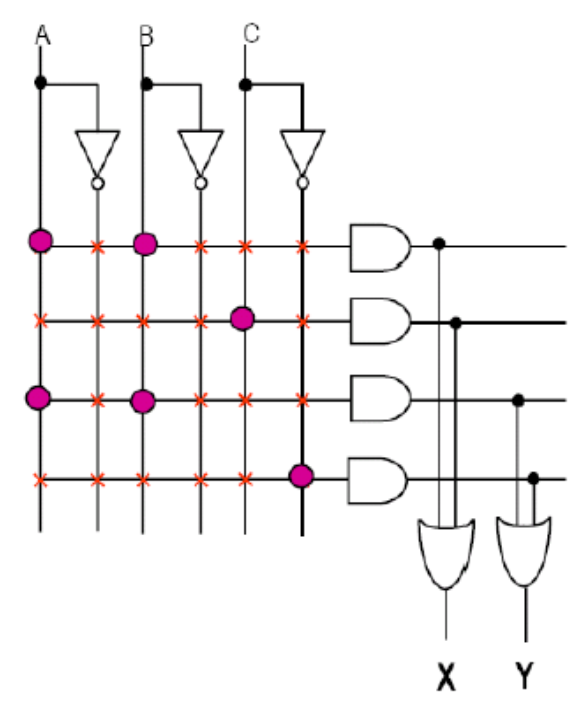

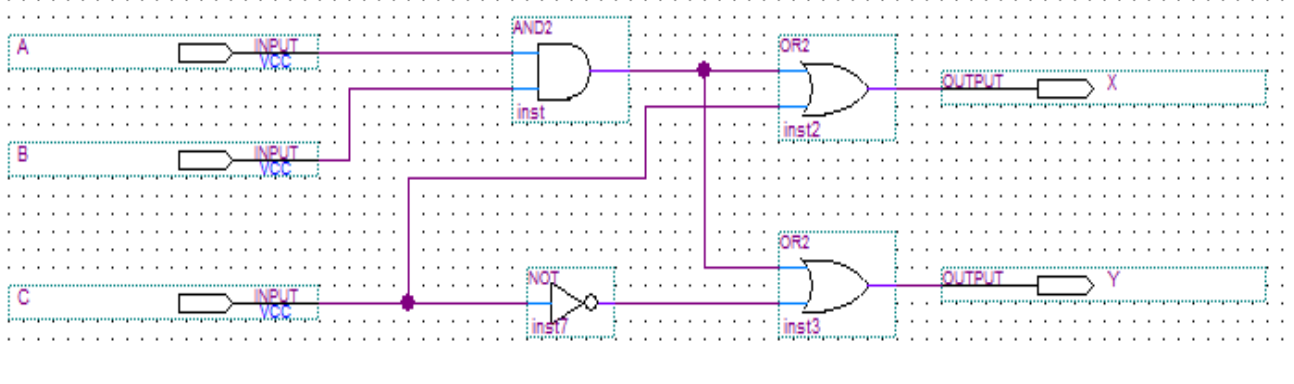

Soit deux simples équations logiques à programmer:

\$ Y = A.B + bar(C)\$

Nous remarquons que seule la partie contenant les ET est 'programmable". Les points rouges représentent les connexions conservées.

Programmation.

Pour programmer ces composants, il existe des logiciels et matériels spécifiques. Nous pouvons réaliser la programmation en compilant soit :

-

Une réalisation graphique.

-

Un code écrit en langage VHDL.

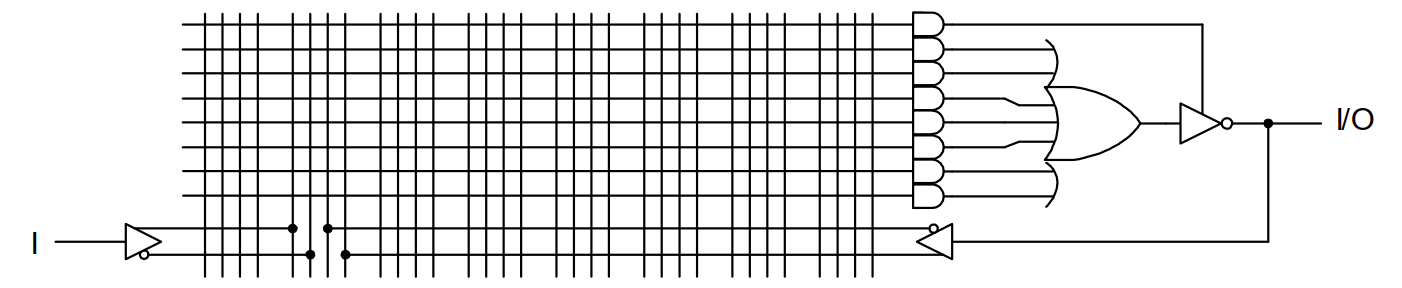

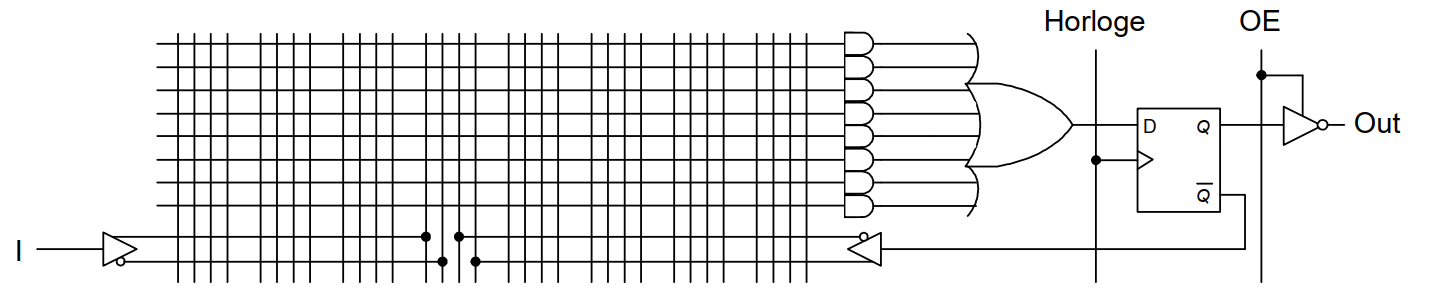

Les différents types de sortie d’un PLD:

-

Structure de sorties combinatoires :

Ces sorties 3 états sont rebouclées vers la matrice de fusibles. En mode haute impédance, on peut utiliser une broche de sortie comme étant une variable d’entrée intermédiaire :

-

Structure de sortie séquentielle :

Ces sorties utilisent des bascules D dont les sorties sont de type trois états. Elles sont contrôlées par un signal de validation OE (Output Enable) et une horloge commune à toutes les bascules :

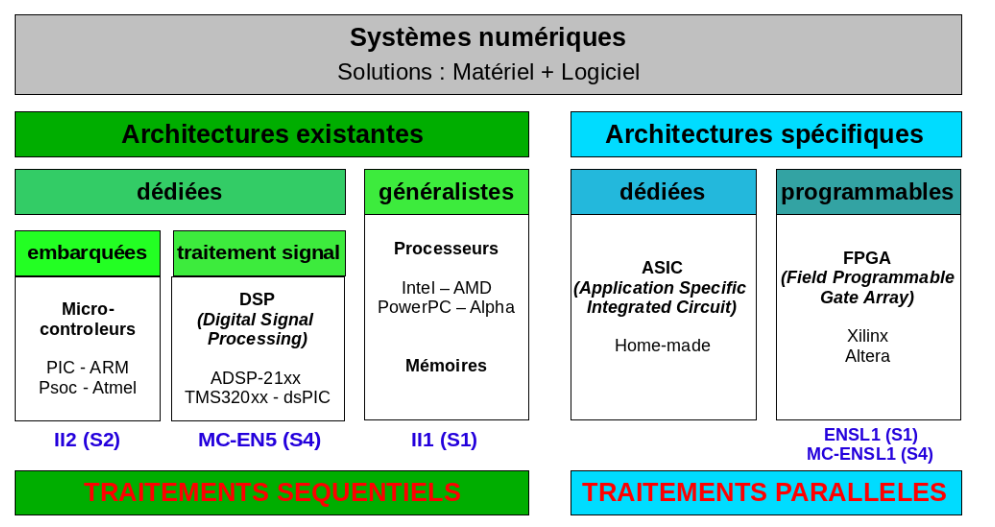

Evolution.

Les systèmes logiques programmables évoluent énormément, nous trouvons mainteant trois grandes catégories de systèmes logiques programmables :

-

les CPLD(Complex Programmable Logic Device)

-

les FPGA(Field Programmable Gate Array)

-

les ASIC(Application Specific Integrated Circuit).

La desciption de ces catégories sera développée dans un autre module.

Voici un tableau pour nous situer dans le monde des systèmes numériques.

|

Il est important de comprendre que suivant le projet à réaliser, on devra choisir entre une architecture existante ou spécifique. |

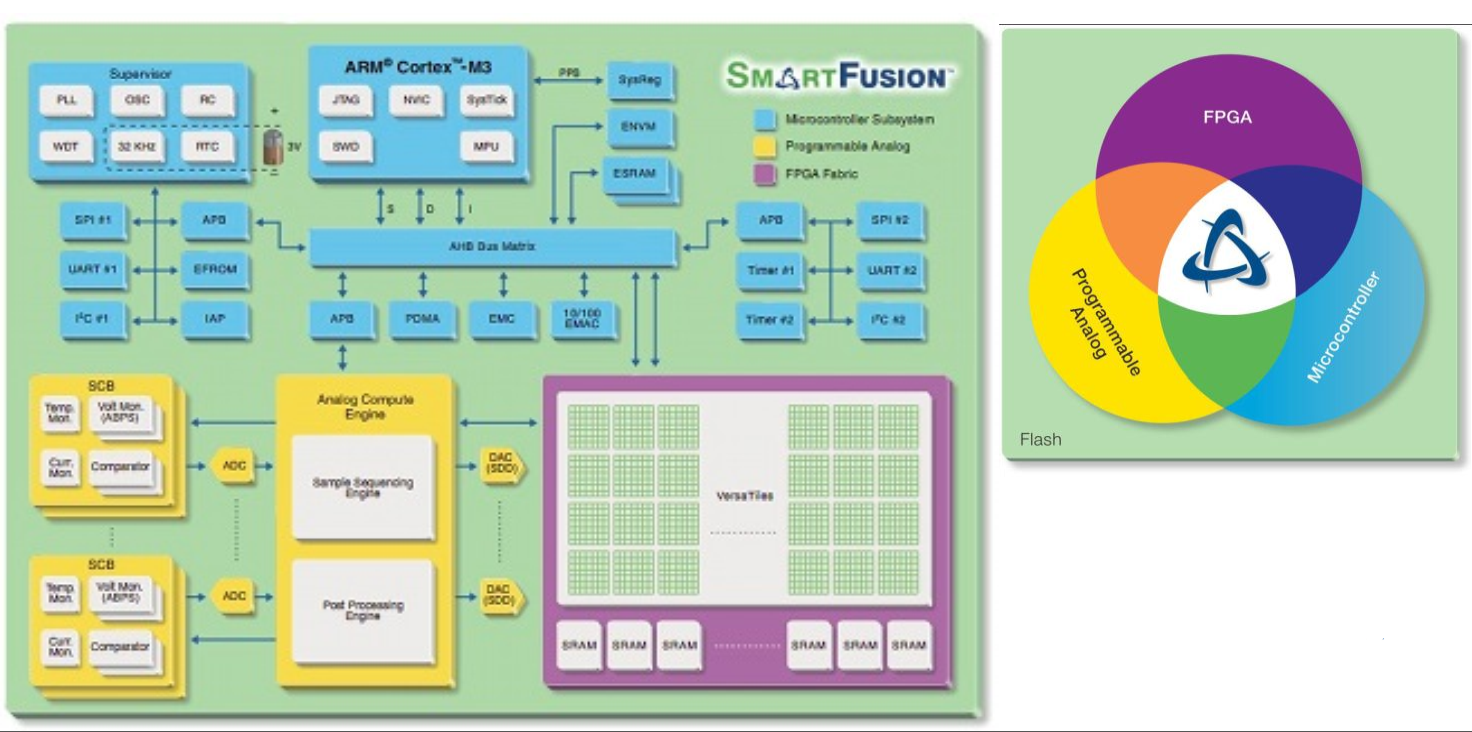

Cependant l’innovation technologique permet maintenant un mélange des deux architectures avec les SoC System On Chip. On intégre un microcontroleur dans un système logique programmable.

Conclusion.

Nous avons vu dans ce cours le principe de la mémorisation avec des circuits logiques. Nous savons maintenant que la bascule est la fonction de base de la logique séquentielle. Nous avons découvert plusieurs technologies de bascules. L’association de ces bascules a permis ensuite de réaliser des fonctions plus complexes comme les compteurs, les registres et enfin les mémoires.

L’avancée technologique dans l’intégration, toujours plus importante, des fonctions mémoires a permis également d’envisager la technologie des fonctions logiques programmables. Cette technologie a permis d’intégrer sur une même puce des systèmes numériques complexes, limitant les coûts et les risques de pannes. Enfin les derniers progrès, nous ont permis de découvrir les SoC.

Bibliographie:

Sciences et Technologies Électriques de: LAJOUAD RACHID et HANAFI AHMED.

GEII Créteil Vitry